Packaging SbS et couche HPB: Samsung repense le refroidissement des Exynos

Samsung prépare des SoC Exynos avec packaging côte à côte (SbS) et couche HPB: meilleure dissipation pour CPU et DRAM, attendus sur la gamme Galaxy Z.

Samsung prépare des SoC Exynos avec packaging côte à côte (SbS) et couche HPB: meilleure dissipation pour CPU et DRAM, attendus sur la gamme Galaxy Z.

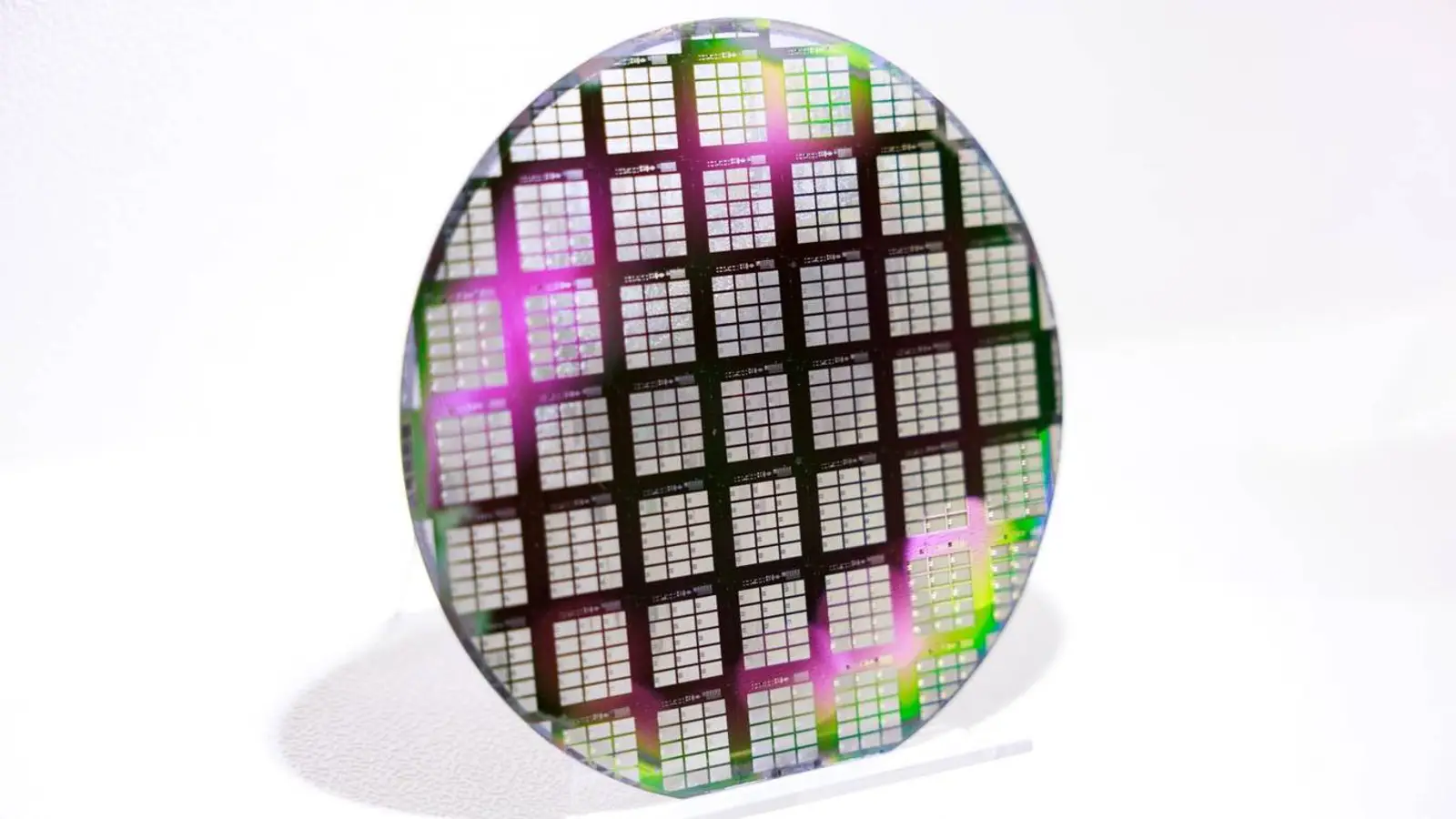

© D. Novikov

Samsung prépare une nouvelle manière d’améliorer le refroidissement de ses processeurs mobiles Exynos. Selon des sources, le groupe envisage une disposition d’encapsulation dite côte à côte (SbS), capable de faire baisser sensiblement la température et d’optimiser l’efficacité énergétique des prochains SoC.

Longtemps critiqués pour la surchauffe et une consommation élevée, les Exynos affichent toutefois des progrès tangibles ces dernières années. L’Exynos 2600, par exemple, adopte la technologie Heat Path Block (HPB), une fine couche de cuivre qui accélère l’évacuation de la chaleur depuis la matrice. Aujourd’hui, les puces Exynos s’appuient sur un boîtier de type FOWLP, où les contacts sont déportés au-delà de la matrice, ce qui atténue les contraintes thermiques — non sans contreparties. Le point sensible demeure l’empilement: la RAM et la couche HPB sont positionnées au-dessus du processeur. Dans cette configuration, la chaleur quitte efficacement la puce, mais l’échauffement de la DRAM reste moins maîtrisé — un compromis qui n’a jamais totalement convaincu. La structure SbS vise précisément à corriger cela.

Avec cette architecture côte à côte, le processeur et la DRAM prennent place l’un à côté de l’autre, tandis que la couche HPB recouvre simultanément les deux. L’idée est d’accélérer la dissipation thermique à la fois du bloc de calcul et de la mémoire, tout en réduisant l’épaisseur de l’empilement — un paramètre crucial pour les smartphones les plus fins.

Reste un compromis: quand l’épaisseur diminue, l’encombrement s’accroît à l’horizontale. Si les fabricants d’appareils n’y voient pas un frein majeur, Samsung pourrait adopter durablement le boîtier SbS pour Exynos. On s’attend d’ailleurs à voir les premiers processeurs avec ce design dans la série Galaxy Z, où chaque fraction de millimètre compte et où repenser la gestion thermique apparaît comme une décision pragmatique.