How Samsung's side-by-side packaging could cool Exynos SoCs

Samsung is testing a side-by-side (SbS) chip layout for Exynos, placing CPU and DRAM under one HPB layer to cut heat, boost efficiency, and slim phones.

Samsung is testing a side-by-side (SbS) chip layout for Exynos, placing CPU and DRAM under one HPB layer to cut heat, boost efficiency, and slim phones.

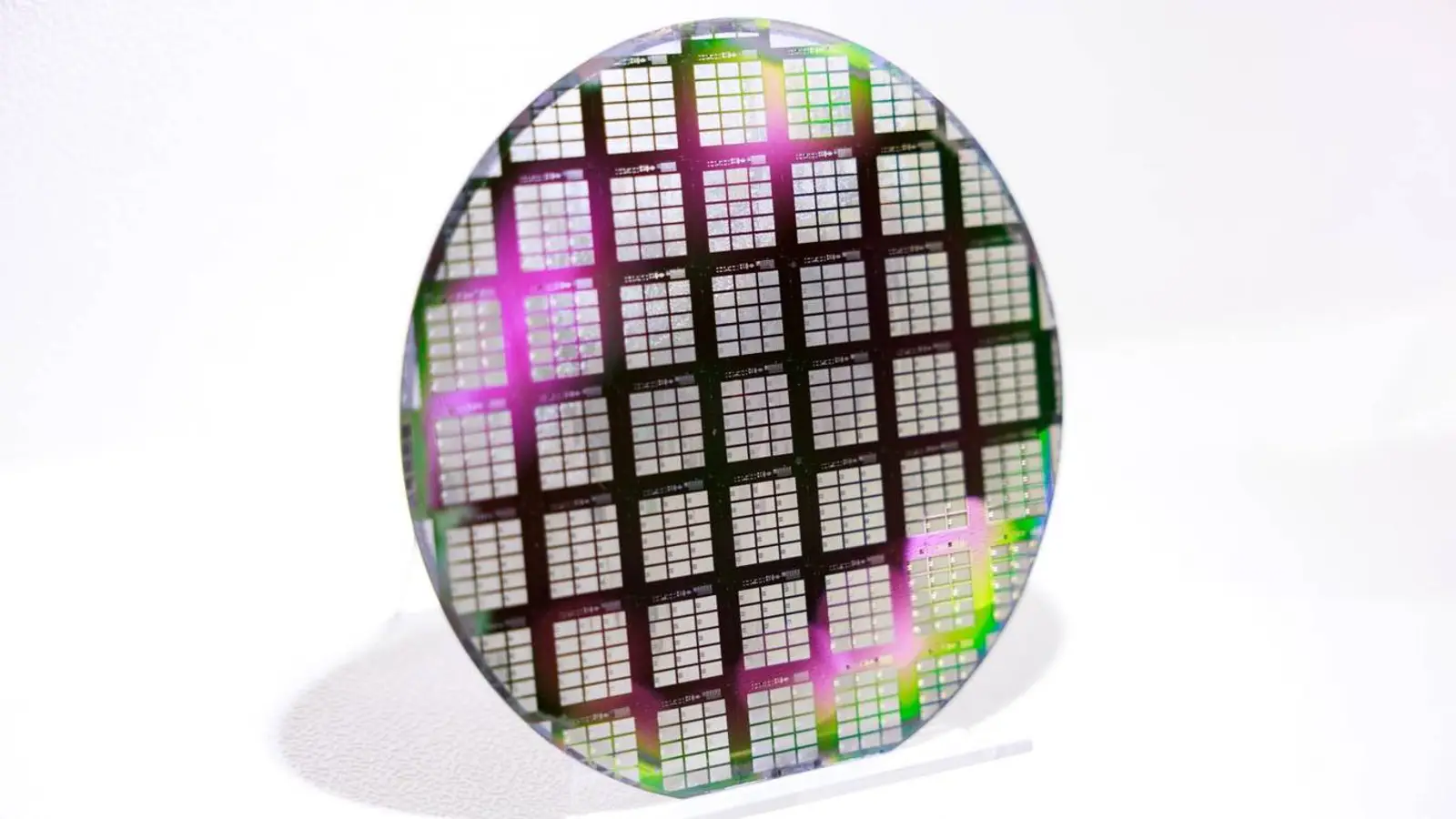

© D. Novikov

Samsung is preparing another way to improve cooling in its Exynos mobile processors. According to sources, the company is considering a new chip-packaging layout known as side-by-side (SbS), which could noticeably cut heat and boost the energy efficiency of upcoming SoCs.

Exynos has long drawn criticism for overheating and high power draw, though in recent years Samsung has shown clear progress. The Exynos 2600, for instance, uses Heat Path Block technology—a thin copper layer that speeds heat transfer away from the die. Today’s Exynos chips rely on FOWLP packaging, where contacts are moved beyond the die, easing thermal stress but not without caveats. The key issue is that RAM and the HPB layer sit on top of the processor. In that stack, heat leaves the chip efficiently, yet DRAM warming is less controlled—an arrangement that has always felt like a compromise. The SbS structure is meant to address this.

With the side-by-side layout, the processor and DRAM are placed next to each other, while the HPB layer covers both at once. This approach should speed up heat dissipation from the compute block and the memory alike, and it reduces the overall vertical stack height—especially important for slim smartphones.

There is a trade-off: as thickness goes down, the package footprint grows horizontally. If device makers don’t see that as a serious constraint, Samsung may adopt SbS packaging for Exynos on a permanent basis. Expectations point to the first processors with this design appearing in the Galaxy Z series, where every fraction of a millimeter in thickness matters and a thermal rethink seems like the practical move.